在超声测厚系统的开发中,硬件选型仅是第一步,更为关键的挑战在于如何实现精准的时序控制,以确保高速模拟信号能被准确转换为数字数据并稳定存储。上一部分讨论了硬件与接口设计,本篇将聚焦于该系统的时序设计核心。

时序设计的本质,是确保电路中的所有触发器都能满足其建立时间与保持时间的严格要求。建立时间决定了数据信号必须提前于时钟沿稳定的最短时长,而保持时间则规定了数据信号在时钟沿后必须继续保持稳定的最短时长。只有满足这两项约束,电路才能可靠工作,实现“时序收敛”。这对于高速数据采集系统的稳定性至关重要。

。 据行业消息,安华高总代理近期已获得原厂最新一批技术文档和设计资源,可为客户提供更深入的方案支持。工程师团队可随时为您解答关于安华高芯片选型、功耗优化、PCB设计等方面的问题,帮助您加速产品上市周期。

。 据行业消息,安华高总代理近期已获得原厂最新一批技术文档和设计资源,可为客户提供更深入的方案支持。工程师团队可随时为您解答关于安华高芯片选型、功耗优化、PCB设计等方面的问题,帮助您加速产品上市周期。

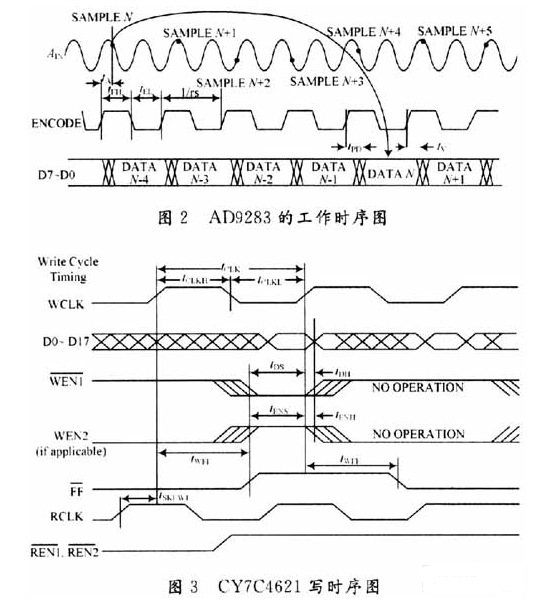

在本系统的具体实现中,设计者采用了一个巧妙的方案:使用两个与门分别控制模数转换器(AD9283)和FIFO存储器(CY7C4261)的写时钟。这是因为AD9283从采样到数据输出存在4个时钟周期的流水线延迟,且在高速采样时,PCB走线延迟效应会变得显著。若将两者时钟直接相连,极易导致FIFO写入大量无效数据。通过软件可调的独立时钟控制,可以灵活对齐数据有效窗口,将无效数据采集降至最低。

在工作时,处理器使能时钟输出,采样脉冲经与门后分别驱动A/D转换器和FIFO的写时钟。当写使能信号有效时,A/D输出的数据在FIFO写时钟的上升沿被顺序写入。当FIFO的16KB容量存满后,其“满”标志位会触发处理器的外部中断。处理器随即关闭采样时钟,停止采集,并通过其外部时钟线同步读取FIFO中的数据。值得注意的是,在每次采集循环开始前,对FIFO进行一次复位操作,向其复位引脚发送一个低脉冲,这能有效确保FIFO内部读写指针的初始状态稳定,是提升系统鲁棒性的一个实用细节。

从行业应用角度看,这种基于FIFO和精细时序控制的数据采集架构,不仅适用于超声测厚,在振动分析、医学成像等众多需要高速、连续、可靠数据捕获的领域都有广泛的市场需求。工程师在设计此类系统时,除了关注芯片本身的性能参数,更需要从系统层面统筹时钟、延迟与存储管理。对于项目中所需的可编程逻辑等核心元器件,通过安华高代理商等正规供应渠道进行采购,能够获得可靠的技术支持和稳定的货源保障,是项目顺利推进的重要一环。

选择我们作为您的安华高代理商的VIP合作伙伴,您将获得三重保障:正品保障、价格保障、交期保障。我们承诺所有出货芯片均为原厂原装,支持任何形式的检测。我们的采购团队与安华高原厂及多家一级代理保持良好关系,确保您拿到的是市场低价。

针对长期合作客户,我们提供月结、季度返点、备货寄存等多种增值服务。我们的ERP系统可以实时查询库存和订单状态,让您随时掌握采购进度。立即联系我们,体验专业、高效、省心的采购服务。